-

Notifications

You must be signed in to change notification settings - Fork 18k

New issue

Have a question about this project? Sign up for a free GitHub account to open an issue and contact its maintainers and the community.

By clicking “Sign up for GitHub”, you agree to our terms of service and privacy statement. We’ll occasionally send you account related emails.

Already on GitHub? Sign in to your account

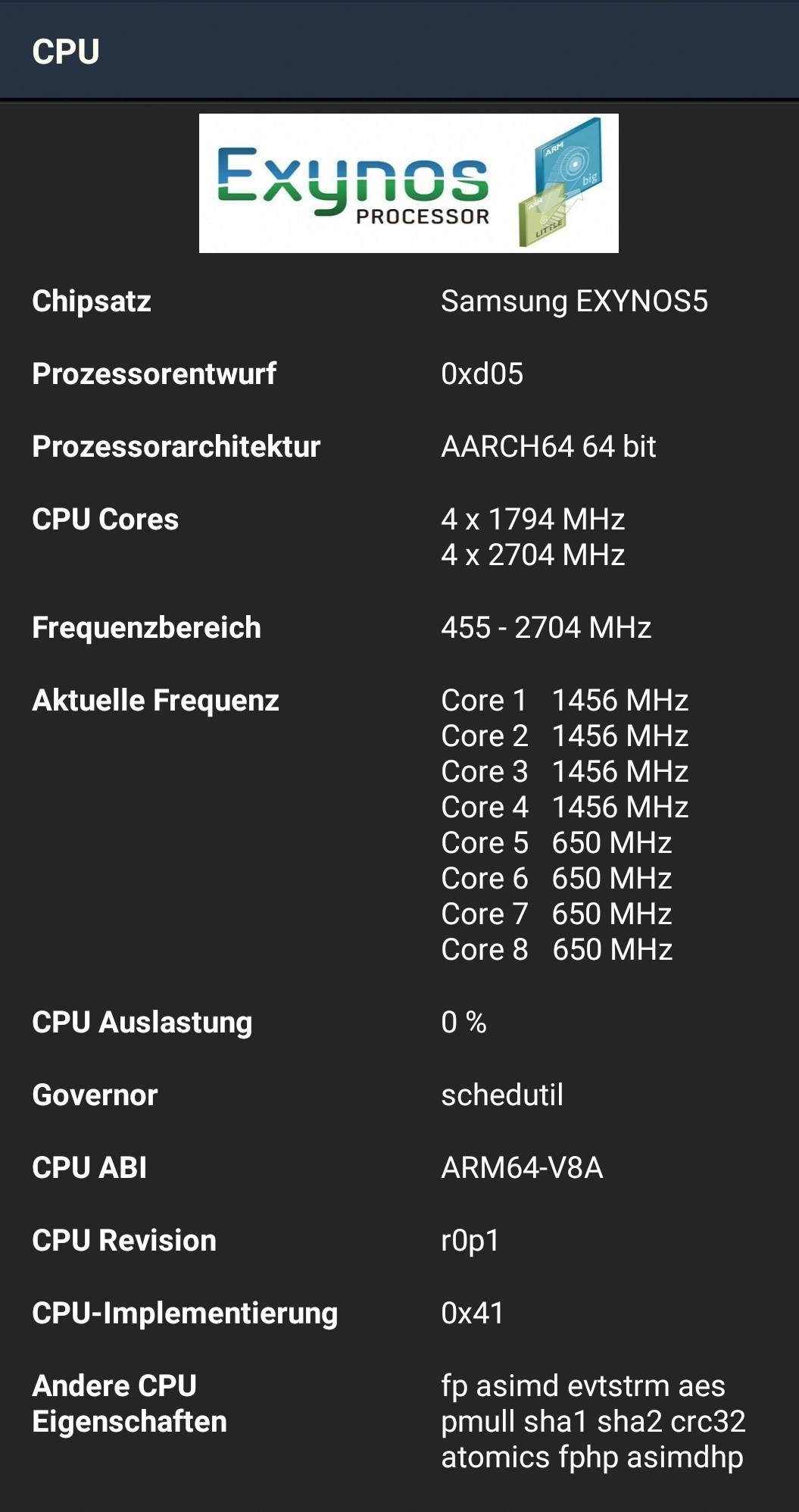

cmd/compile: go binaries not working on exynos 64 bit CPUs #28431

Comments

|

Seems like a likely culprit. I see "atomics" on your list of cpu features. That's the feature we're using to guard the new instruction. |

|

How can I help to find that out? |

|

Read the docs for that new instruction (LDADDAL)? |

|

We've encountered the error only in the 64 bit version, compiling it with 32 bit support only worked perfectly. |

All cores seem to support atomics (flags are set).

They do

This goes a little beyond my capabilities. |

|

Reading through the ARM manual (https://static.docs.arm.com/ddi0487/ca/DDI0487C_a_armv8_arm.pdf) I suspect there is a check in ID_AA64ISAR0_EL1 (PDF page 2518) for the Arm 8.1 atomics missing. |

|

Also a hint is the CPU info from the device: as you can see the small cores are ARM 8.0 and the big cores are 8.1.

Seems like your first suspicion was right, while they all support atomics, LDADDAL is only available on Arm 8.1, not 8.0. |

That's expected, the new instruction is only used for 64-bit builds.

Well, they claim to. We should test that claim. Can you write some assembly with a LDADDAL instruction in it, compile and run it? No Go, just C and/or assembly.

I took a look and it seems ok at first glance, but the Go arm64 disassembler gives up on the instruction in question, so I can't be sure. I need access to the platform disassembler. Could you build this program ( |

|

We could add a test for the CPU variant if there's an easy way to get it. I wish the OS didn't lie to us and present the |

|

Here is the object dump |

|

Thanks. That code looks correct to me. |

|

@randall77 the only way I can think of would be for the C code to put itself in a |

|

Also, ARM documentation states that the big and little cores must have the same instruction support. Therefore, this is really a hardware bug. Unfortunately, it is a widespread bug. Source: https://developer.arm.com/technologies/big-little Clarification: The 4 big cores in the Samsung Exynos 9810 are custom Mongoose 3 cores which support

|

|

If we can confirm that the Go compiler is doing this right, then the best solution may be to report this to Samsung. The most reasonable fix I can think of would be updating the kernel to report the lowest common feature denominator instead of that of the local core. |

|

I agree, this isn't a bug in Go. It's a bug in the feature set reported by the kernel. |

|

Update: I have made a minimal C example of this. It is available on a gist: https://gist.github.com/jadr2ddude/aee7b47a91b70ee3dd75cad97e5ff4e0 Also on twitter: https://twitter.com/CompuJad/status/1057744906943377408 |

|

Even though it's a bug in the kernel or hardware, I think Go should avoid triggering it. It seems gomobile (1.11) programs are completely broken on one of the most widely used Android phones. |

|

We have also experienced this behaviour, however only in debug binaries. We could not trigger it with release binaries (somehow). |

|

In order to detect this, we would need to read |

|

Change https://golang.org/cl/147377 mentions this issue: |

|

The easy sledgehammer is disabling the optimization if runtime.GOOS == "android". @gopherbot please consider this for backport to 1.11. It's an unavoidable crash on a popular Android phone and easy to avoid from Go. |

|

Backport issue(s) opened: #28586 (for 1.11). Remember to create the cherry-pick CL(s) as soon as the patch is submitted to master, according to https://golang.org/wiki/MinorReleases. |

|

I don't have a Samsung S9+ to test CL 147377. Can someone with the offending hardware verify the fix? |

|

I can confirm that it works now (android app built with gomobile and this Go version). |

|

Update: the kernel problem was resolved in an update. The kernel no longer reports support for atomics. Image from @noxer of my atomics test. |

Go binaries have stopped working on Galaxy S9+. The breaking commit seems to be 0a7ac93.

What version of Go are you using (

go version)?go 1.11.1 (worked in go 1.10.4)

Does this issue reproduce with the latest release?

Yes

What operating system and processor architecture are you using (

go env)?Android on Arm64 (Android 8.0 on a Galaxy S9+)

What did you do?

Used

gomobileto compile the following code and used it in an Android app to display a toast notification.What did you expect to see?

The app displaying a Toast with the text "Hello: "

What did you see instead?

The app crashing with a SIGILL.

Credits

The problem was brought to our attention in the gophers slack channel by @shipit.

Git bisect output

The text was updated successfully, but these errors were encountered: